#### Department of Electronics and telecommunication Engineering

## VLSI WORKSHOP

### **REPORT**

DATED- 01/09/2018-02/09/2018

Time: 09:30-06:00

#### Address: MGM's College of Engineering and Technology Kamothe, Navi Mumbai.

#### **ABOUT: - Workshop Conducted Over VLSI**

VLSI (Very Large Scale Integrated Circuits) workshop by Skill Inc. in association with IEEE MGMCET Student Branch, Bombay Section. Skill Inc. provide technical skill trainings, industry exposure and all-round career growth for students and institutions via our knowledge partners also a platform for training companies and individual trainers to share their knowledge and grow by maximising their reach. Skill Inc. in association with IEEE MGMCET Student Branch keeping up with its vision to provide a platform to the students for gaining skills, knowledge and help them develop themselves in an all-round fashion for their career growth, organized Workshop on VLSI Design at MGMCET. Main goals of workshop were Designing a VLSI product, About Vlsi, Better understanding of Timing analysis, Run LTSpice simulations by students and testing circuit made by students itself, Fabrication process using Lambda rule, Design rules for scaling, designing universal gates in microwind software. The intended audience is students enrolled in the workshop. Students of second year, Third Year, Final Year EXTC attended the lecture. The workshop was delivered by Ms. Vridhi shah, Mr. Shubham Vishwakarma. The faculty present was Mrs. Neda Khan and from Skill Inc. Md Sanaullah Khan and Adarsh Pandey graced the student with their presence throughout the seminars.

#### **ABOUT** The Department: - Electronics and telecommunication Engineering

**Vision -** To produce world class Technocrats, Scientists & Entrepreneurs with new ideas & innovations to meet cost effective industry expectations for all sections of society.

#### Mission –

1. To develop & deliver quality academic programs in emerging & innovative field of Engineering to empower the students to meet Industry Standards.

2. To motivate students to develop innovative solutions for betterment of society.

3. To Create Centre of Excellence by establishing the Incubation Centers to meet global research challenges.

We Started with Introductory session by Respected Ms. Vridhi shah, Shubham Vishwakarma Sir who introduced the students to the vast Field of VLSI also the overview of the two day workshop.

Fig 1 - Beginning of VLSI Workshop

Fig 2 – Shubham Sir giving overview of VLSI

Fig 3- Vridhi shah Mam Teaching about MOSFETs

Fig 4 – Volunteers Helping students in Doubts

Fig 5 – Rahul Sir Solving some Doubts

Fig 6 – Rahul Sir Teaching

In lecture/workshop Trainers discussed the Following:-

- 1. In Overview the Trainers gave a short description about:

- a) What you will learn???

- b) What is ICs?

- c) Classification of ICs.

- d) What is VLSI?

- e) MOSFET

- f) Types of MOSFET

- g) Comparison of n- and p-type MOSFETs.

Fig 7 – Students doing LTSpice Simulation

| lenitda |  |      |            |   |  |   | 王術書(今) |           |     |      |  |   |   |     |        |  |  |  |  |  |  |  |

|---------|--|------|------------|---|--|---|--------|-----------|-----|------|--|---|---|-----|--------|--|--|--|--|--|--|--|

| citra   |  |      |            |   |  |   |        |           |     |      |  |   |   |     | Vdd+   |  |  |  |  |  |  |  |

|         |  |      |            |   |  |   |        |           |     |      |  |   |   |     |        |  |  |  |  |  |  |  |

|         |  | . Vd | <u>d++</u> |   |  |   |        | (internet | Σ   |      |  | - |   |     |        |  |  |  |  |  |  |  |

|         |  |      |            |   |  |   |        |           |     |      |  |   |   |     |        |  |  |  |  |  |  |  |

|         |  |      |            |   |  |   |        |           |     |      |  |   |   |     |        |  |  |  |  |  |  |  |

|         |  |      |            |   |  |   |        |           |     |      |  |   |   |     |        |  |  |  |  |  |  |  |

|         |  |      |            |   |  |   |        |           |     |      |  |   |   |     |        |  |  |  |  |  |  |  |

|         |  | , ru | NPUT       | 1 |  |   |        |           |     | πρυτ |  | 1 |   | .0. | clock2 |  |  |  |  |  |  |  |

|         |  |      |            |   |  | × |        | 5         | 181 |      |  | D | a |     |        |  |  |  |  |  |  |  |

|         |  |      |            |   |  |   |        |           |     |      |  |   |   |     |        |  |  |  |  |  |  |  |

|         |  |      |            |   |  |   |        |           |     |      |  |   |   |     |        |  |  |  |  |  |  |  |

|         |  |      |            |   |  |   |        |           | ĺs  |      |  |   |   |     |        |  |  |  |  |  |  |  |

|         |  |      |            |   |  |   |        |           | 14  |      |  |   |   |     |        |  |  |  |  |  |  |  |

|         |  |      |            |   |  |   |        |           |     |      |  |   |   |     |        |  |  |  |  |  |  |  |

|         |  |      |            |   |  |   |        |           |     |      |  |   |   |     |        |  |  |  |  |  |  |  |

#### Fig 7 & 8 – LTSpice and Microwind Simulations

- 2. Moore's Law

- 3. CMOS Inverter & Various Logic Gates

- 4. Simulation of Universal gates on Ltspice

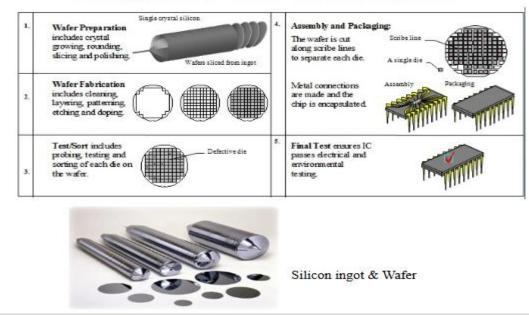

- 5. Stages of IC Fabrication

- 6. Design Rules for Microwind

Fig 9- Shubham Sir Solving Doubts

Fig 10 - Students Simulating Microwind

# **Stages of IC Fabrication**

Fig 11.Stages of IC Fabrication.

During the workshop, few students asked questions regarding the topic and were very satisfied with the answer from Trainers. They concluded their talk by insisting the students and faculty to plan for visit to IIT-Bombay to see the fabrication process. Also, Adarsh Pandey Sir extended thanks to all the IEEE volunteers, Neda Khan Mam for organizing the workshop. All the Trainers were given a Token of Appreciation and the trainees were awarded with Certificates.

Fig 12- Token Of Appreciation To Skills.Inc

Fig 13 – Token of Appreciation to Trainers

Fig 14 – Trainers, Faculty and IEEE Members

Fig 15– END of the workshop Picture of Trainers, Faculty and Certified Students

We thank The Management, The Principal, The HOD, Trainers, Participants and supporting faculty's for their support. Attendance –39 Students, 13 IEEE Volunteers, 2 Faculty members, 4 Trainers.